TU Graz entwickelt Hardware-Architektur für Post-Quantum-Kryptographie

Post-Quantum-Sicherheitsalgorithmen in Hardware zu integrieren, galt bislang als Herausforderung. Ein Forschungsteam der TU Graz hat dafür eine einheitliche Hardware mit zusätzlichen Sicherheitsmaßnahmen entwickelt.

Noch sind sie nicht Realität, aber in nicht allzu ferner Zukunft werden ausgereifte, leistungsstarke Quantencomputer zur Verfügung stehen. Sie werden Bereiche wie künstliche Intelligenz, Finanzmodellierung, Medikamentenentwicklung, Wettervorhersagen und Verkehrsoptimierung revolutionieren, bergen allerdings auch ein Risiko im Bereich der Cybersecurity. Ein rechenstarker Quantencomputer wird in der Lage sein, zahlreiche kryptographische Algorithmen zu brechen, die zur Absicherung der digitalen Welt essentiell sind. Darum sind bereits einige quantensichere Algorithmen in Entwicklung, sogenannte „Post-Quantum Cryptography (PQC)“-Algorithmen. Sie in elektronische Geräte zu implementieren, stellte bislang allerdings ein Problem dar. Im Projekt PQC-SRC hat ein Team unter der Leitung von Sujoy Sinha Roy vom Institut für angewandte Informationsverarbeitung und Kommunikationstechnologie (IAIK) der TU Graz eine Hardware für diese PQC-Algorithmen entwickelt und weitere Sicherheitsmaßnahmen implementiert. Die Forschenden standen dabei auch im Austausch mit Unternehmen wie Intel und AMD.

Unter den neu entwickelten Algorithmen gelten jene als besonders vielversprechend, die auf Rechenproblemen mit mathematischen Gitterstrukturen basieren. Diese Rechenprobleme zu lösen gilt auch für Quantencomputer als unmöglich. Im Zuge seiner Standardisierung für Post-Quanten-Kryptographie hat das National Institute for Standards and Technology (NIST) in den USA ein Schlüsselkapselungsverfahren (lattice-based key encapsulation oder KEM) mit dem Namen „Kyber“ und drei digitale Signaturalgorithmen, „Dilithium“, „Falcon“ und den am IAIK mitentwickelten „SPHINCS+“, ausgewählt. KEM-Algorithmen erlauben es zwei kommunizierenden Parteien, sich sicher auf einen geheimen Schlüssel zu einigen. Digitale Signaturalgorithmen ermöglichen es einem Empfänger, die Authentizität der empfangenen Nachrichten zu verifizieren.

Notwendigkeit für sicheres und effizientes Design

Nach der Bekanntgabe der standardisierten PQC-Algorithmen bereiten sich Organisationen, Wirtschaft und Industrie für den Umstieg auf die quantensichere Kryptographie vor. Das bedeutet, alle Geräte müssen von klassischen KEM- und Signaturverfahren auf ihre post-quanten-tauglichen Pendants umgestellt werden. Daher ist es notwendig, dass die neu standardisierten PQC-Algorithmen auf einer möglichst großen Bandbreite an Elektrogeräten einsetzbar sind.

Um den Umstieg auf die quantensichere Kryptographie möglichst störungsfrei zu gestalten, sind sichere und effiziente Design- und Implementationsmethoden notwendig. Die Forschenden des Cryptographic Engineering Teams unter der Leitung von Sujoy Sinha Roy am IAIK haben solche Methoden entwickelt und dabei besonderes Augenmerk auf elektronische Geräte mit geringen Ressourcen gelegt.

Entwicklung eines hardwarebasierten Coprozessors für standardisierte Post-Quanten-Kryptographie

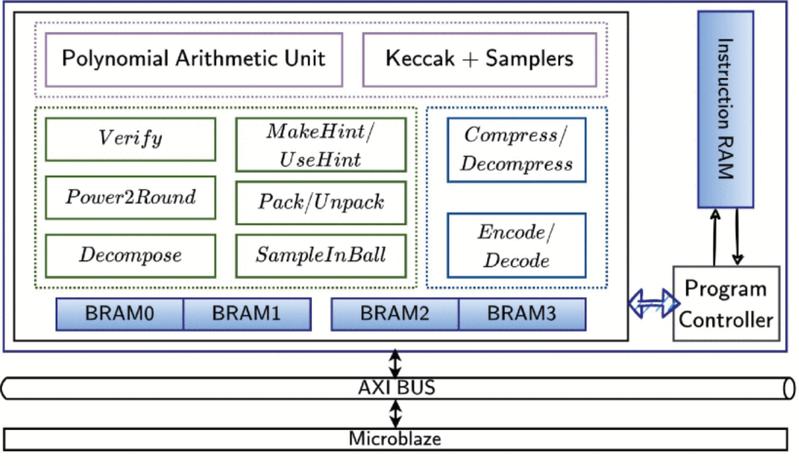

Ein Ergebnis dieser Forschung ist die Konstruktion eines einheitlichen kryptographischen Coprozessors namens „KaLi“, der sowohl das Schlüsselkapselungsverfahren „Kyber“ als auch den digitalen Signaturalgorithmus „Dilithium“ unterstützt. Dieses einheitliche Design ist für sichere Kommunikationsprotokolle wie das weit verbreitete Transport Layer Security (TLS) unerlässlich, da dabei Schlüsselkapselung und digitale Signaturen zum Einsatz kommen. Eine der größten Herausforderungen bei der Entwicklung war es, das Design des Coprozessors kompakt zu halten, weil die PQC-Algorithmen mehr Speicher und Recheneinheiten als konventionelle Kryptographie benötigen. Wird das Design diesen Effizienzanforderungen nicht gerecht, könnten viele Geräte mit begrenzten Ressourcen, wie beispielsweise in IoT- oder Smart-Card-Anwendungen, nicht mehr verwendet werden. Zudem muss die Prozessorarchitektur agil und flexibel bleiben – das ermöglicht Änderungen der kryptographischen Algorithmen aufgrund zukünftiger Bedrohungen ohne Hardware-Tausch.

Neben der Effizienz und der Kompaktheit ist auch die physische Sicherheit einer kryptographischen Implementierung wichtig. So mögen die mathematischen Probleme hinter einem Algorithmus bekannten Angriffen standhalten, doch auch die physikalischen Eigenschaften eines Computers, etwa Wärmeschwankungen, elektromagnetische Strahlung oder Energieverbrauch, können sensible Informationen preisgeben. Angreifer könnten etwa Mithilfe einer Antenne herausfinden, was in einem Gerät vor sich geht. Darum erarbeitete das Forschungsteam Techniken, um Systeme auch vor solchen Angriffen zu schützen. Dabei entstand die Datenrandomisierungstechnik „Kavach“. Diese optimiert den Rechenaufwand durch die Nutzung spezieller Zahleneigenschaften, die in den Rechenoperationen der Algorithmen genutzt werden. Die Technik können Kryptographen nun dazu nutzen, Post-Quanten-Algorithmen für KEM und Signaturen zu entwickeln, die besser gegen physikbasierte Angriffe geschützt sind.

Wichtiger Schritt für Unternehmen und Organisationen

„Wir haben in den vergangenen fünf Jahren große Sprünge im Bereich der Quantenprozessoren gesehen“, sagt Sujoy Sinha Roy. „Wenn leistungsfähige Quantencomputer fertig entwickelt sind, wären sie in der Lage, Verschlüsselungen in einigen Sekunden aufzubrechen, für die herkömmliche Computer Jahre bräuchten. Das ist gefährlich für Banktransaktionen, staatliche Verteidigungssysteme und vieles weitere. Dies wird gerne als Quanten-Apokalypse bezeichnet und die möchten wir verhindern. Da Unternehmen und Organisationen sich auf den Wechsel zur Post-Quanten-Kryptographie vorbereiten, liefern unsere Forschungsergebnisse einen weiteren wichtigen Schritt in Richtung dieser Transition.“

Dieses Projekt wurde von der Semiconductor Research Corporation gefördert und ist im Field of Expertise „Information, Communication & Computing“ verankert, einem von fünf wissenschaftlichen Stärkefeldern der TU Graz.

Wissenschaftlicher Ansprechpartner:

Sujoy SINHA ROY

Assoc.Prof. PhD

TU Graz | Institut für Angewandte Informationsverarbeitung und Kommunikationstechnologie

Tel.: +43 316 873 5501

sujoy.sinharoy@tugraz.at

Originalpublikation:

A Unified Cryptoprocessor for Lattice-Based Signature and Key-Exchange https://doi.org/10.1109/TC.2022.3215064

High-Speed Design of Post Quantum Cryptography With Optimized Hashing and Multiplication https://doi.org/10.1109/TCSII.2023.3273821

Die semantisch ähnlichsten Pressemitteilungen im idw